## **RAPID COMMUNICATION • OPEN ACCESS**

## Demonstration of $\beta$ -Ga $_2$ O $_3$ nonvolatile flash memory for oxide electronics

To cite this article: Vishal Khandelwal et al 2023 Jpn. J. Appl. Phys. 62 060902

View the article online for updates and enhancements.

## You may also like

- A state-of-art review on gallium oxide fieldeffect transistors

Rundi Qiao, Hongpeng Zhang, Shuting Zhao et al.

- -Ga<sub>2</sub>O<sub>3</sub> for wide-bandgap electronics and optoelectronics Zbigniew Galazka

- <u>Progress in state-of-the-art technologies of Ga<sub>2</sub>O<sub>3</sub> devices</u> Chenlu Wang, Jincheng Zhang, Shengrui Xu et al.

https://doi.org/10.35848/1347-4065/acdbf3

## Demonstration of $\beta$ -Ga<sub>2</sub>O<sub>3</sub> nonvolatile flash memory for oxide electronics

Vishal Khandelwal<sup>1</sup>, Manoj Kumar Rajbhar<sup>1</sup>, Glen Isaac Maciel García<sup>1</sup>, Xiao Tang<sup>1</sup>, Biplab Sarkar<sup>2</sup>, and Xiaohang Li<sup>1\*</sup>

<sup>1</sup>Advanced Semiconductor Laboratory, Electrical, and Computer Engineering Program, CEMSE Division, King Abdullah University of Science and Technology (KAUST), Thuwal 23955-6900, Saudi Arabia

Received April 13, 2023; revised June 3, 2023; accepted June 5, 2023; published online June 20, 2023

This report demonstrates an ultrawide bandgap  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> flash memory for the first time. The flash memory device realized on heteroepitaxial  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> film had TiN as the floating gate (FG) and Al<sub>2</sub>O<sub>3</sub> as tunneling and gate oxides. A memory window of > 4 V was obtained between the programmed and erased states of the device. The memory states showed negligible degradation in threshold voltage (V<sub>TH</sub>) even after 5000 s, exhibiting excellent nonvolatility. Furthermore, the device showed a V<sub>TH</sub> of  $\sim$ 0.3 V after applying a 17 V programming voltage pulse, indicating the potential of the electron trapping phenomenon in the FG to achieve enhancement-mode operation in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> transistors for high-power and logic applications. This study would provide insights for future oxide electronics integrating  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> memory.

© 2023 The Author(s). Published on behalf of The Japan Society of Applied Physics by IOP Publishing Ltd

(Ultra)wide bandgap oxides have tremendous application potential in transparent and flexible electronics, high power and RF electronics, UV photonics, and extreme environment electronics. 1-4) To date, several oxide semiconductors such as indium gallium zinc oxide,<sup>5)</sup> In<sub>2</sub>O<sub>3</sub>,<sup>6)</sup> and β-Ga<sub>2</sub>O<sub>3</sub><sup>7)</sup> have been widely explored in numerous applications including solid-state displays, thin-film transistors, power devices, and UV photodetectors. Among them, ultrawide bandgap  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (E<sub>G</sub>  $\sim 4.9 \, eV$ ) has emerged as a promising candidate, especially for realizing oxide electronics, due to its superior properties including high-quality epitaxial films, wide n-type doping range from semi-insulating to highly conducting films, high chemical, and thermal stability. <sup>7,8)</sup> So far, β-Ga<sub>2</sub>O<sub>3</sub>-based power transistors,9) Schottky diodes, 10) and solar-blind photodetectors<sup>11)</sup> have been extensively studied. However, β-Ga<sub>2</sub>O<sub>3</sub>-based memory devices are also required for realizing oxide electronics.

For memory devices, β-Ga<sub>2</sub>O<sub>3</sub>-based resistive randomaccess memory (RRAM) has been investigated. 12,13) However, the filamentary behavior of β-Ga<sub>2</sub>O<sub>3</sub> RRAMs and their precise control remains unclear. Moreover, β-Ga<sub>2</sub>O<sub>3</sub> RRAMs will require integration with an appropriate selector device<sup>14,15)</sup> indicating a considerate effort is indispensable to achieve commercial maturity. Meanwhile, flash memory devices are a highly scalable alternative that exhibits substantial maturity due to decades of exploration. 16,17) Furthermore, trapping of electrons in the floating gate (FG) is a promising approach to realize enhancement-mode (E-mode) operation to get normally-OFF transistor operation. 18-20) Thus, the development of β-Ga<sub>2</sub>O<sub>3</sub>-based flash memory devices is deemed to play a pivotal role in realizing future oxide electronics for various application fields.

In this work, we demonstrated a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>-based nonvolatile flash memory device using TiN metal as the FG. The virgin devices exhibited a normally-ON behavior, whereas positive and negative voltage pulses were applied for programming and erasing operation, respectively. A large memory of >4 V was obtained between the programming

and erasing state with memory retention of  $> 5000 \, \mathrm{s}$ . A large program bias is shown to shift the threshold voltage ( $V_{TH}$ ), thereby promoting the E-mode operation. The  $\beta\text{-}\mathrm{Ga_2O_3}$  flash memory devices reported in this work showed a large nonvolatile memory window and a desirable memory retention characteristic.

Flash memory devices were fabricated on a 50 nm thick  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> film grown on a c-plane sapphire substrate. A pulsed laser deposition (PLD) system was employed to grow a heteroepitaxial film using a Si-doped  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> target. The growth temperature was maintained at 700 °C, whereas the laser ablation frequency and laser energy were set to 5 Hz and 100 mJ, respectively. The oxygen partial pressure was kept as 4 mTorr during growth. Post-growth, the samples were cleaned thoroughly using acid and acetone-IPA solvent treatment.

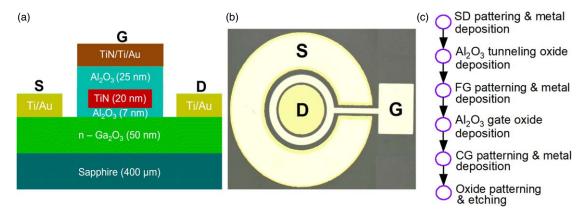

Next, flash memory devices with circular-geometry source/ drain/gate contacts were fabricated. A cross-sectional schematic and top microscopic view of the fabricated devices are shown in Figs. 1(a) and 1(b). First, Ti/Au (20/100 nm) source/drain (SD) ohmic contacts were formed on the β-Ga<sub>2</sub>O<sub>3</sub> film. Metals were deposited using a DC/RF sputtering system and patterned using the standard photolithography and lift-off process. The ohmic contacts were then annealed at 400 °C for 60 s in N<sub>2</sub> ambient. Thereafter, a 7 nm thick Al<sub>2</sub>O<sub>3</sub> layer serving as the tunneling oxide was deposited using an atomic layer deposition (ALD) system at 250 °C. A 20 nm of TiN metal as the FG was then deposited on the tunneling oxide followed by the conventional photolithography and lift-off process for patterning. Next, a 25 nm thick Al<sub>2</sub>O<sub>3</sub> blocking oxide was deposited using ALD at 250 °C. Finally, a TiN/Ti/Au (20/20/70 nm) control gate (CG) was formed using the sputtering and conventional photolithography process. TiN deposition was accomplished using a DC/RF sputtering system having a high-purity Ti target in the N<sub>2</sub> reactive chamber. Finally, the Al<sub>2</sub>O<sub>3</sub> dielectric layer was removed to expose the SD ohmic contacts via BCl<sub>3</sub>-based dry etching. The diameter of the drain contact was kept as 200  $\mu$ m. A donut-shape CG had an inner circle and outer circle diameter of 220 and 280  $\mu$ m, respectively,

<sup>&</sup>lt;sup>2</sup>Department of Electronics and Communication Engineering, Indian Institute of Technology, Roorkee, Uttarakhand, 247667, India

<sup>\*</sup>E-mail: xiaohang.li@kaust.edu.sa

Fig. 1.  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> flash memory device (a) Cross-sectional schematic. (b) Top microscopic view. (c) Fabrication process flow.

indicating the effective (CG) gate length to be 30  $\mu$ m. FG also had a donut-shape geometry (inner circle and outer circle diameter of 240 and 260  $\mu$ m, respectively) and was kept within the boundaries of the CG. CG-to-drain and CG-to-source distances were kept as 10  $\mu$ m and 20  $\mu$ m, respectively. The device fabrication process flow is summarized in Fig. 1(c).

The epitaxial film quality was characterized using X-ray diffraction (XRD) and an atomic force microscope (AFM). The free carrier concentration inside the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> film was measured using a Hall-effect measurement system. Electrical characterization was performed on a temperature-controlled probe station equipped with a Keithley 4200 semiconductor parameter analyzer setup.

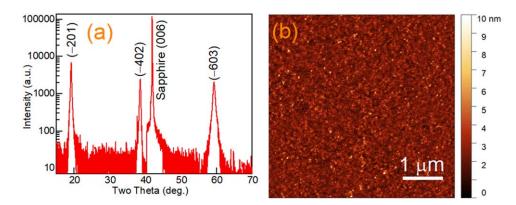

The XRD pattern of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> film exhibited (-201), (-402), and (-603) peaks, as highlighted in Fig. 2(a) which confirms the mono-orientation of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> film on the sapphire substrate. The RMS roughness of the film was observed to be ~0.8 nm indicating a smooth surface morphology, as observed in the AFM image of Fig. 2(b). Based on the Hall-effect measurements, the electron concentration and mobility of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> film were found to be ~5 ×  $10^{18}$  cm<sup>-3</sup> and 0.35 cm<sup>-2</sup> V<sup>-1</sup> s<sup>-1</sup> at RT.

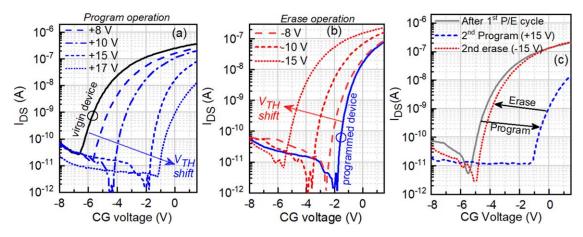

Next, the  $\beta\text{-}Ga_2O_3$  flash memory devices were characterized to validate the nonvolatile memory operation. Figure 3(a) shows the transfer characteristics of the  $\beta\text{-}Ga_2O_3$  flash memory device at  $V_{DS}=1$  V post application of program voltage pulses. The value of  $V_{TH}$  was estimated from the transfer characteristics using the extrapolation in the

linear region method.<sup>21)</sup> The virgin device showed a normally-ON behavior with a  $\ensuremath{V_{TH}}$  of  $-4.5\ \ensuremath{V}.$  Subsequently, the application of different positive voltage pulses to the CG resulted in a positive V<sub>TH</sub> shift, validating the programming operation of the memory, as shown in Fig. 3(a). For instance, a +17 V, 100 ms pulse applied to the CG yields a V<sub>TH</sub> of  $\sim$ 0.3 V. Note that such a positive value of  $V_{TH}$  in an nchannel transistor is identified as a normally-OFF device. For validating the erase operation, a virgin device was initially programmed to a  $V_{TH}$  of 0.3 V followed by the application of negative voltage pulses in the CG. Likewise, a negative V<sub>TH</sub> shift was observed after the erase operation, as observed in Fig. 3(b). To validate the program/erase (P/E) repeatability, a virgin device was initially programmed followed by the erase operation. After the 1st program/erase (P/E) cycle, the device was tested for a 2nd P/E cycle, as highlighted in Fig. 3(c). Note that the virgin device and the device after 1st P/E cycle showed different sub-threshold slopes (SS). This can be attributed to the interface properties which are highly dependent on electron trapping/de-trapping phenomena, thereby influencing the SS after the 1st P/E cycle. Nevertheless, a reasonable P/E cycle repeatability after the 1st P/E cycle confirms the proof-of-concept working  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> flash memory device.

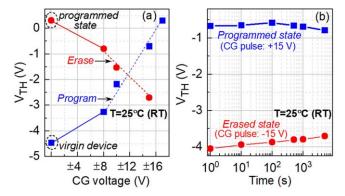

The dependence of the  $V_{TH}$  shift on the program/erase bias voltage is shown in Fig. 4(a). A nonvolatile memory window of greater than 4 V is achieved by applying program/erase pulses of less than 20 V in magnitude. Once programmed or erased, an insignificant  $V_{TH}$  shift was observed even after

Fig. 2. Material quality of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> film on sapphire (a) XRD pattern highlighting the (-201), (-402), and (-603) peaks. (b) AFM surface morphology showing a smooth surface.

Fig. 3. Characteristics of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> flash memory device at RT (a) Program characteristics, (b) Erase characteristics, (c) Program and erase characteristics after 1st P/E cycle.

**Fig. 4.** Characteristics of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> flash memory device at RT of  $T=25\,^{\circ}$  C. (a) Measured V<sub>TH</sub> of the device after the program and erase operations. (b) Retention characteristics.

5000 s, as shown in Fig. 4(b). Thus, the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> flash memory showed excellent charge retention characteristics in its nonvolatile memory states.

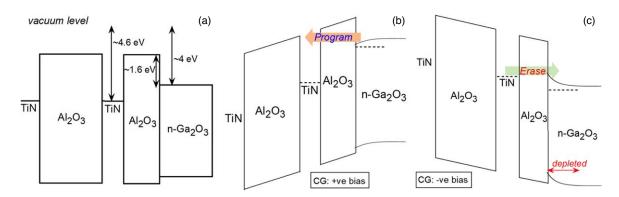

Notably, the increase in  $V_{TH}$  during the program operation was observed to be higher than that during the erase operation [Fig. 4(a)]. For example, a CG pulse of +15 V during the program operation induced an effective  $V_{TH}$  shift ( $\Delta V_{TH}$ ) of  $\sim$ 4 V from the virgin state, whereas a CG bias of -15 V during the erase operation induced an effective  $\Delta V_{TH}$  of  $\sim$ 3 V from the programmed state. We speculate that a lower  $V_{TH}$  shift in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> flash memories during the erase operation was likely caused by the electric field distribution inside the films and carrier tunneling paths. The energy band profiles of the layers of

the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> flash memory layers in isolation (noncontact), during the program operation, and during the erase operation are shown in Figs. 5(a)-5(c), respectively. The work function and band energy details of TiN,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, and Al<sub>2</sub>O<sub>3</sub> can be found elsewhere.  $\overline{^{22-24)}}$  During the program operation, the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> channel is under accumulation. Since the Fermi energy level is close to the conduction band in n-type ultrawide bandgap semiconductors such as  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>, <sup>25)</sup> the program voltage pulse applied to the CG effectively caused a band-bending across the tunneling and blocking oxides, as highlighted in Fig. 5(b). However, the device V<sub>TH</sub> was nearly positive at the programmed state. Thus, a relatively larger area of β-Ga<sub>2</sub>O<sub>3</sub> film under the gate is fully depleted when electrons are stored in the FG after the program operation. Therefore, a portion of the erase voltage pulse applied to the CG was sustained by the depleted  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> film along with the tunneling and blocking oxides, as highlighted in Fig. 5(c). Moreover, to obtain a similar  $V_{TH}$  shift, the desired erase pulse duration was observed to be significantly higher than the program pulse duration (not shown). All of these observations exhibited good agreement with the conventional FG or charge-trap NAND flash memories realized on Si. 17,26) Note that the device  $|V_{TH}|$  after the erase operation was observed to be lower than  $|V_{TH}|$  of the virgin device indicating the erase operation was unable to remove all the electrons injected into the FG during the program operation. Moreover, improving the erase characteristics by hole injection into the FG is an unlikely case for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> flash memories. Traditionally, planar Si flash memories are fabricated on a p-type substrate,<sup>27</sup> whereas 3D-NAND flash memories are fabricated on poly-Si

Fig. 5. Schematics of energy band profile along vertical outline through the CG (a) Isolated (noncontact) layers. During (b) program operation (c) erase operation.

pillars.<sup>28)</sup> During the erase operation, holes can be injected from the channel to the charge-trap layer which is between the tunneling oxide and gate oxide layers.<sup>29,30)</sup> Therefore, the choice of proper hole charge-trap dielectric has been observed to improve the erase characteristics of both planar and 3D Si flash memories.<sup>27,28)</sup> In contrast, a low intrinsic carrier concentration in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> indicates the channel is free from holes during the erase operation. Moreover, obtaining a p-type  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is also a major challenge.<sup>8)</sup> Thus, program and erase operation in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> flash memories are thought to be solely due to electron injection and removal from the FG.

We now discuss the contributions of this work apart from data storage via  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> memory. As observed in Fig. 4(a), a program bias voltage pulse of ≥ 17 V results in a normally-OFF transistor ( $V_{TH} > 0 V$ ). Therefore, a programmed  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> flash memory device can be used to realize standalone normally-OFF low-voltage transistors. Moreover, both high-voltage and lowvoltage power switches are controlled by logic circuitry such as pulse width modulators. Traditionally, Si-based CMOS technology is used to realize this logic control circuitry. However, β-Ga<sub>2</sub>O<sub>3</sub> based all-oxide electronics mandates these circuits to be realized on a native substrate. Unfortunately, the nonavailability of appropriate p-type doping in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> poses a major hindrance in realizing CMOS logic operations. Interestingly, many of these logic control circuitries can be realized using a combination of normally-ON and normally-OFF transistors.<sup>31)</sup> Thus, the logic circuitry for controlling the β-Ga<sub>2</sub>O<sub>3</sub> power converters can be realized using a suitable connection of virgin/erased (normally-ON) β-Ga<sub>2</sub>O<sub>3</sub> flash memory device with a programmed (normally-OFF) β-Ga<sub>2</sub>O<sub>3</sub> flash memory device. Consequently, the power converters and their logic control circuitry can be monolithically integrated into a standalone  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrate. Finally, the flash memories reported in this work were fabricated on a foreign substrate indicating the compatibility of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> flash memory devices with low-cost heterogeneous integration schemes. Note that the devices investigated in this work were free from the post-deposition annealing (PDA) step. However, PDA has been observed to minimize the trap density at the Al<sub>2</sub>O<sub>3</sub>/β-Ga<sub>2</sub>O<sub>3</sub> interface thereby improving the overall interface quality.  $\overline{^{32,33)}}$  Therefore, a realistic  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> flash memory processing may require a PDA step to obtain a good tunnel oxide interface—which is critical for memory operations.

In summary, we demonstrated  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> flash memory transistors using a TiN metal FG. A large nonvolatile memory window of > 4 V was observed between the programmed and erased states. The memory exhibited an insignificant threshold voltage shift in the programmed and erased states even after 5000 s. Finally, the realization of enhancement-mode operation by storing electrons in the FG is thought to be promising for realizing multiple essential devices of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> electronics.

**Acknowledgments** The KAUST researchers are grateful for KAUST Nanofabrication Corelab and funding support of the Baseline Fund BAS/1/1664-01-01, Near-term Grand Challenge Fund REI/1/4999-01-01, and Impact Acceleration Fund REI/1/5124-01-01.

ORCID iDs

Vishal Khandelwal

https://orcid.org/0000-0003-1759

1209

Glen Isaac Maciel García

https://orcid.org/0000-0002-2574

0545

Biplab Sarkar

https://orcid.org/0000-0003-0074-0626

- 1) M. Lorenz et al., J. Phys. D: Appl. Phys. 49, 433001 (2016).

- 2) X. Tang et al., ACS Appl. Mater. Interfaces 14, 1304 (2022).

- X. Tang, Y. Lu, R. Lin, C.-H. Liao, Y. Zhao, K.-H. Li, N. Xiao, H. Cao,

W. Babatain, and X. Li, Appl. Phys. Lett. 122, 121101 (2023).

- 4) Y. Lu et al., ACS Appl. Mater. Interfaces 14, 47922 (2022).

- 5) Y. Zhao et al., Adv. Funct. Mater. 30, 2003285 (2020).

- 6) O. Bierwagen, Semicond. Sci. Technol. 30, 024001 (2015).

- 7) A. J. Green et al., APL Mater. 10, 029201 (2022).

- M. H. Wong and M. Higashiwaki, IEEE Trans. Electron Devices 67, 3925 (2020).

- S. J. Pearton, J. Yang, P. H. Cary IV, F. Ren, J. Kim, M. J. Tadjer, and M. A. Mastro, Appl. Phys. Rev. 5, 011301 (2018).

- A. Jadhav, L. A. M. Lyle, Z. Xu, K. K. Das, L. M. Porter, and B. Sarkar, J. Vac. Sci. Technol. B 39, 040601 (2021).

- X. Chen, F.-F. Ren, J. Ye, and S. Gu, Semicond. Sci. Technol. 35, 023001 (2020).

- 12) W. Li, J. Wan, Z. Tu, H. Li, H. Wu, and C. Liu, Ceram. Int. 48, 3185

- C.-C. Yang, J.-Q. Huang, K.-Y. Chen, P.-H. Chiu, H.-T. Vu, and Y.-K. Su, IEEE Access 7, 175186 (2019).

- 14) J. Zhou, K.-H. Kim, and W. Lu, IEEE Trans. Electron Devices 61, 1369

- S. Kim, J. Zhou, and W. D. Lu, IEEE Trans. Electron Devices 61, 2820 (2014).

- 16) A. Chen, Solid-State Electron. 125, 25 (2016).

- B. Sarkar, N. Ramanan, S. Jayanti, N. D. Spigna, B. Lee, P. Franzon, and V. Misra, IEEE Electron Device Lett. 35, 48 (2014).

- 18) D. Biswas, C. Joishi, J. Biswas, P. Tiwari, and S. Lodha, Appl. Phys. Lett. 117, 172101 (2020).

- 19) B. Hou et al., IEEE Electron Device Lett. 39, 397 (2018).

- 20) Z. Feng et al., IEEE Electron Device Lett. 41, 333 (2020).

- A. Ortiz-Conde, F. J. García Sánchez, J. J. Liou, A. Cerdeira, M. Estrada, and Y. Yue, Microelectron. Reliab. 42, 583 (2002).

- 22) F. A. Noor, M. Abdullah, Sukirno, Khairurrijal, A. Ohta, and S. Miyazaki, J. Appl. Phys. 108, 093711 (2010).

- L. A. M. Lyle, K. Jiang, E. V. Favela, K. Das, A. Popp, Z. Galazka,

G. Wagner, and L. M. Porter, J. Vac. Sci. Technol. A 39, 033202 (2021).

- 24) T. Kamimura, K. Sasaki, M. Hoi Wong, D. Krishnamurthy, A. Kuramata, T. Masui, S. Yamakoshi, and M. Higashiwaki, Appl. Phys. Lett. 104, 192104 (2014).

- S. Mukhopadhyay, L. A. M. Lyle, H. Pal, K. K. Das, L. M. Porter, and B. Sarkar, J. Appl. Phys. 131, 025702 (2022).

- 26) Y. Park et al., 2006 Int. Electron Devices Meeting, 2006, p. 1.

- 27) Y. Q. Wang, W. S. Hwang, G. Zhang, G. Samudra, Y.-C. Yeo, and W. J. Yoo, IEEE Trans. Electron Devices 54, 2699 (2007).

- W. Y. Choi, H. S. Kwon, Y. J. Kim, B. Lee, H. Yoo, S. Choi, G.-S. Cho, and S.-K. Park, IEEE Electron Device Lett. 38, 164 (2017).

- S. Jeon, J. H. Han, J. Lee, S. Choi, H. Hwang, and C. Kim, IEEE Electron Device Lett. 27, 486 (2006).

- 30) B. Choi et al., Semicond. Sci. Technol. 33, 10LT01 (2018).

- V. Khandelwal, S. Yuvaraja, G. I. M. García, C. Wang, Y. Lu, F. AlQatari, and X. Li, Appl. Phys. Lett. 122, 143502 (2023).

- 32) M. Hirose et al., Microelectron. Eng. 216, 111040 (2019).

- H. Zhou, S. Alghmadi, M. Si, G. Qiu, and P. D. Ye, IEEE Electron Device Lett. 37, 1411 (2016).