A Precision, Energy-Efficient, Oversampling, Noise-Shaping Differential SAR Capacitance-to-Digital Converter

About

Abdulaziz Alhoshany, et al., "A Precision, Energy-Efficient, Oversampling, Noise-Shaping Differential SAR Capacitance-to-Digital Converter" IEEE Transactions on Instrumentation and Measurement, 68 (2), 2019, 392.

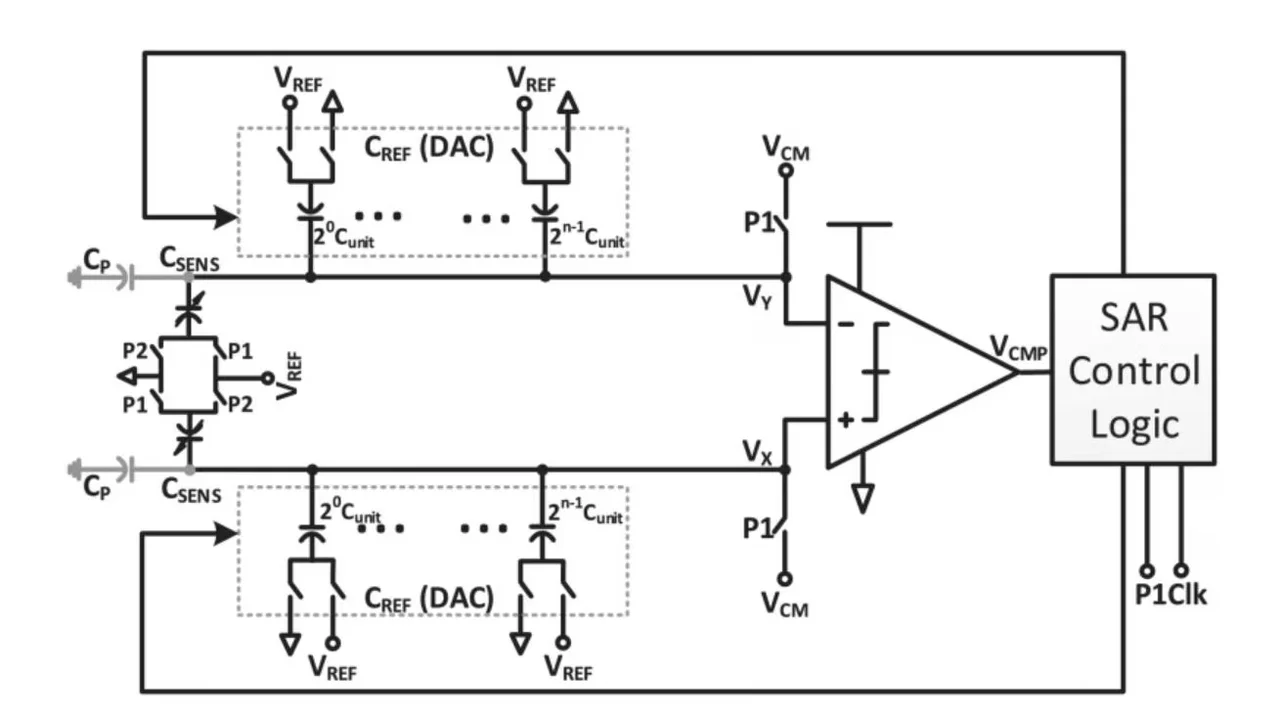

This paper introduces an oversampling, noise-shaping differential successive-approximation-register capacitance-to-digital converter (CDC) architecture for interfacing capacitive sensors. The proposed energy-efficient CDC achieves high-precision capacitive resolution by employing oversampling and noise shaping. The switched-capacitor (SC) integrator is inserted between the comparator and the charge-redistribution digital-to-analog converter to implement noise shaping and to make the interface circuit insensitive to parasitic capacitances. An inverter-based operational transconductance amplifier with a common-mode feedback circuit is employed to implement the SC integrator with subthreshold biasing for low voltage and low power. The ring-oscillator-based comparator is implemented to achieve high energy efficiency. The test chip is fabricated in a 0.18-μm CMOS technology. The proposed CDC experimentally achieves 150 aF absolute resolution and 12.74ENOB with an oversampling ratio of 15 and a sampling clock of 18.51 kHz. The fabricated prototype dissipates 1.2 and 0.39 μW from analog and digital supplies, respectively, with an energy efficiency figure-of-merit of 187 fJ/conversion step.