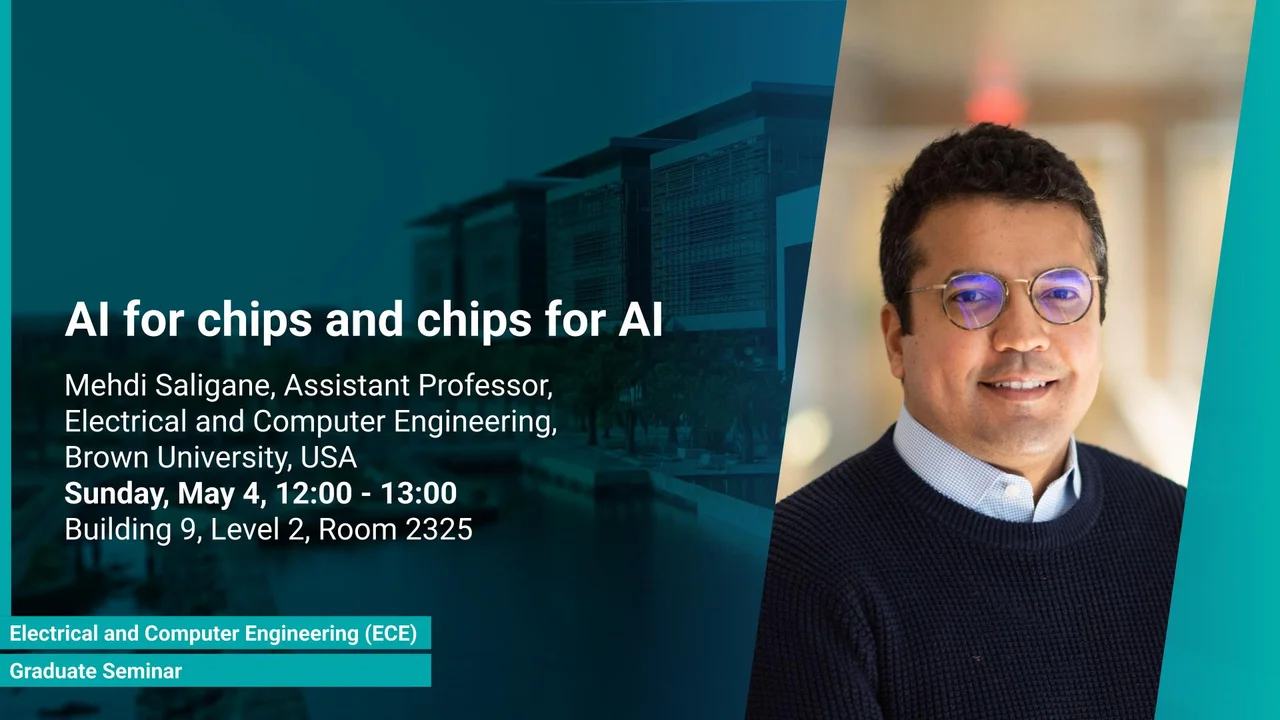

AI for Chips and Chips for AI

This seminar presents a unified "AI for Chips & Chips for AI" approach, demonstrating how AI enhances semiconductor design while specialized silicon accelerates AI computation, creating a rapid innovation cycle.

Overview

The exploding scale of modern applications is stretching yesterday’s integrated-circuit (IC) design flows beyond their limits. This talk presents a unified, open, and highly-automated paradigm — AI for Chips & Chips for AI — that simultaneously (i) harnesses artificial intelligence to build better silicon and (ii) architects silicon that runs AI better.

AI for Chips - Traditional analog layout still relies on expert heuristics. We introduce Agentic-RL gLayout, a goal-conditioned reinforcement-learning agent that replaces hand-tuned placement and routing with policy-driven planning, action, and self-correction. The agent ingests high-level objectives, observes the evolving layout state, and chooses between primitive commands and high-level macros. Positive rewards track goal attainment; penalties capture DRC violations, area bloat, and parasitics, producing cleaner, compact, and rule-compliant layouts without manual intervention. Built atop open-source engines such as OpenROAD, Open Se Cura, and OpenFASoC, the framework pushes layout quality while democratizing access to sophisticated analog design automation.

Chips for AI - Conversely, deploying large language model (LLM) workloads at the edge demands silicon tuned for extreme efficiency. We unveil a hardware–software co-design stack centered on ConSmax, a highly parallel, element-wise alternative to Softmax that slashes latency and energy. By co-optimizing network topology, arithmetic precision, and accelerator micro-architecture, the framework meets sub-millisecond deadlines, preserves privacy, and cuts cloud dependence.

Finally, this talk will walk through an open chip design infrastructure augmented with LLM-guided code, circuits, and layout generation that turns hardware creation into a rapid feedback loop—AI sharpens the tools; tailored accelerators speed AI. Tape-outs in wearables and digital health, cryogenic circuits, and nanofabrication test chips now take weeks instead of months, closing the “AI-for-chips, chips-for-AI” cycle and propelling the next wave of semiconductor innovation.

Presenters

Mehdi Saligane, Assistant Professor, Electrical and Computer Engineering, Brown University, USA

Brief Biography

Mehdi Saligane received the B.S. and M.S. degrees in Electrical Engineering Systems and Industrial Computing from École Polytechnique de Grenoble in 2009, and the M.S. Degree in electrical engineering from the University of Grenoble in 2011, and the Ph.D. degree in Electrical Engineering and Computer Science from the University of Aix-Marseille (IM2NP), France, in 2016. From 2010 to 2015, he was part of the Central Research and Development Group at STMicroelectronics in Crolles, France, focusing on adaptive, ultra-low-power digital design. In 2015, he joined the Michigan Integrated Circuit Laboratory at the University of Michigan, Ann Arbor, MI, USA, as a visiting research investigator. In 2019, he served as a Visiting Researcher at the University of California, San Diego, San Diego, CA, USA. He is a founding member of both the OpenROAD and OpenFASOC Projects. Since 2020, he has been a Research Faculty member at the University of Michigan. In 2024, he joined Google Research as a Visiting Faculty Member, and in 2025, he joined Brown University as an Assistant Professor of Electrical and Computer Engineering. His research interests include secure low-power and energy-efficient IC design, Biosensors, analog/mixed-signal design automation and open-source EDA, and custom architectures for lightweight language model accelerators. Dr. Saligane is the recipient of the 2023 Google Cloud Research Innovators Award and the 2021 Google Research Faculty Award. He served in leadership roles at the CHIPS Alliance from 2020 to 2023, including as Chair of the Analog Working Group and as a member of the Technical Steering Committee. Since 2020, he has served on the IEEE Solid-State Circuits Society (SSCS) Open-Source Ecosystem (TC-OSE) Technical Committee and has been the Chair since 2025. In addition, he co-founded and organizes the SSCS Chipathon Design Contest and the SSCS Code-a-Chip Notebook Competition at ISSCC and VLSI Symposium, fostering student engagement with open-source chip design.