Abstract

Nowadays, integrated circuits (IC) are mostly implemented using Complementary Metal Oxide Semiconductor (CMOS) transistor technology. This technology has allowed the chip industry to shrink the transistors and thus increase the device density, circuit complexity, operation speed, and computation power of the ICs. However, in recent years, the scaling of the transistor has faced multiple roadblocks, which will eventually lead the scaling to an end as it approaches the physical and economic limits. The dominance of sub-threshold leakage, which slows down the scaling of threshold voltage VTH and the supply voltage VDD, has resulted in high power density on the chips. Furthermore, even widely popular solutions such as parallel and multi-core computing have not been able to fully address that problem. These drawbacks have overshadowed the benefits of transistor scaling. With the dawn of the Internet of Things (IoT) era, the chip industry needs adjustments towards ultra-low-power circuits and systems. In this thesis, energy-efficient Micro-/Nano-electromechanical (M/NEM) relays are introduced, their nonleaking property and abrupt switch ON/OFF characteristics are studied, designs and applications in the implementation of ultra-low-power integrated circuits and systems are explored. The proposed designs compose of core building blocks for any functional microprocessor, for instance, fundamental logic gates; arithmetic adder circuits; sequential latch, and flip-flop circuits; input/output (I/O) interface data converters, including an analog-to-digital converter (ADC) and a digital-to-analog converter (DAC); system-level power management DC-DC converters and energy management power-gating scheme. Another contribution of this thesis is the study of device non-ideality and variations on the functionality of circuits. We have thoroughly investigated energy-efficient approximate computing with non-ideal transistors and relays for the next generation of ultra-low-power VLSI systems.

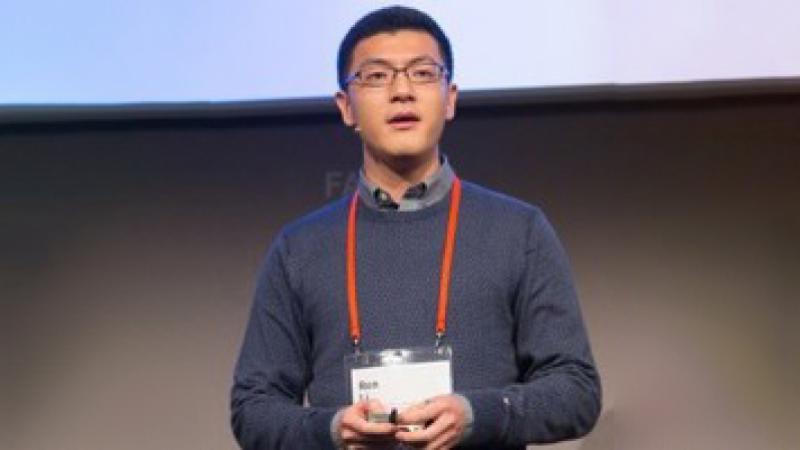

Brief Biography

Ren Li is a Ph.D. candidate in the Integrated Circuits and Systems group at King Abdullah University of Science and Technology (KAUST) under the supervision of Professor Hossein Fariborzi. He received his B.S. degree in electrical engineering and its automation (advanced class) from North China Electric Power University, Beijing, China, in 2014 and his M.S. degree in power engineering from Nanyang Technological University (NTU), Singapore, in 2015. His research interests include Ultra-low-power integrated circuits and systems design, Micro- / Nanoelectromechanical Systems (M/NEMS) IC design and fabrication, Novel devices for next generation computing.