Hesham Omran, et al., "A 33fJ/Step SAR capacitance-to-digital converter using a chain of inverter-based amplifiers". IEEE Transactions on Circuits and Systems I: Regular Papers, 64(2), 2017, 310.

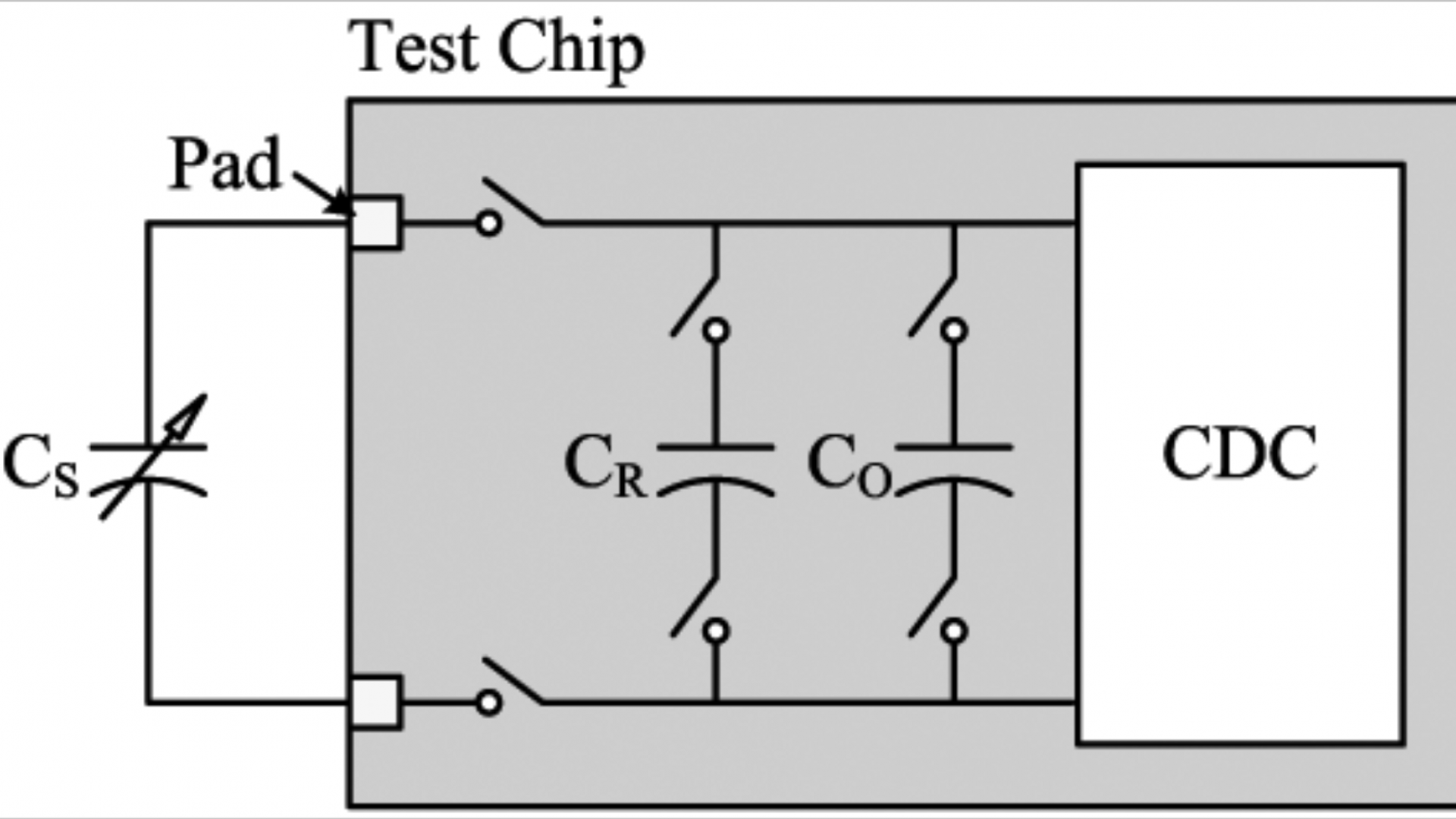

Abstract: A 12 - bit energy-efficient capacitive sensor interface circuit that fully relies on capacitance-domain successive approximation (SAR) technique is presented. Analysis shows that for SAR capacitance-to-digital converter (CDC) comparator offset voltage will result in parasitic-dependent conversion errors, which necessitates using an offset cancellation technique. Based on the presented analysis, a SAR CDC that uses a chain of cascode inverter-based amplifiers with near-threshold biasing is proposed to provide robust, energy-efficient, and fast operation. A hybrid coarse-fine capacitive digital-to-analog converter (CapDAC) achieves 11.7 - bit effective resolution, and provides 83% area saving compared to a conventional binary weighted implementation. The prototype fabricated in a 0.18μm CMOS technology is experimentally verified using MEMS capacitive pressure sensor. Experimental results show an energy efficiency figure-of-merit (FoM) of 33fJ/Step which outperforms the state-of-the-art. The CDC output is insensitive to analog references; thus, a very low temperature sensitivity of 2.3ppm/°C is achieved without the need for calibration.