Abdulaziz Alhoshany, et al., " A 45.8 fJ/Step, energy-efficient, differential SAR capacitance-to-digital converter for capacitive pressure sensing". Sensors and Actuators A: Physical, 245, 2016, 10.

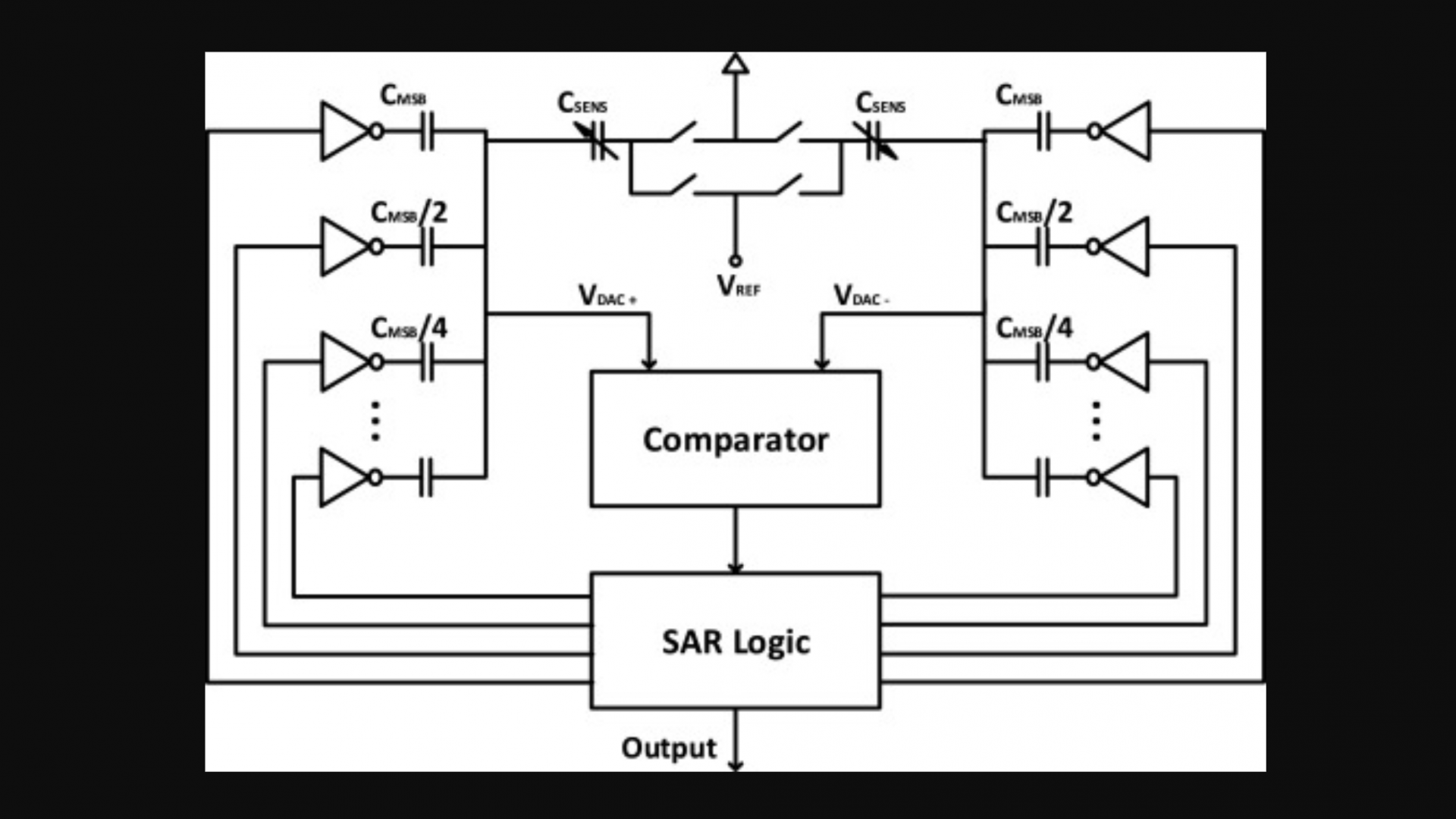

An energy-efficient readout circuit for a capacitive sensor is presented. The capacitive sensor is digitized by a 12-bit energy efficient capacitance-to-digital converter (CDC) that is based on a differential successive-approximation architecture. This CDC meets extremely low power requirements by using an operational transconductance amplifier (OTA) that is based on a current-starved inverter. It uses a charge-redistribution DAC that involves coarse-fine architecture. We split the DAC into a coarse-DAC and a fine-DAC to allow a wide capacitance range in a compact area. It covers a wide range of capacitance of 16.14 pF with a 4.5 fF absolute resolution. An analog comparator is implemented by cross-coupling two 3-input NAND gates to enable power and area efficient operation. The prototype CDC was fabricated using a standard 180 nm CMOS technology. The 12-bit CDC has a measurement time of 42.5 μs, and consumes 3.54 μW and 0.29 μW from analog and digital supplies, respectively. This corresponds to a state-of-the-art figure-of-merit (FoM) of 45.8 fJ/conversion-step.