Hesham Omran, et al., "7.9 pJ/step energy-efficient multi-slope 13-bit capacitance-to-digital converter." IEEE Transactions on Circuits and Systems II: Express Briefs 61 (8), 2014, 589.

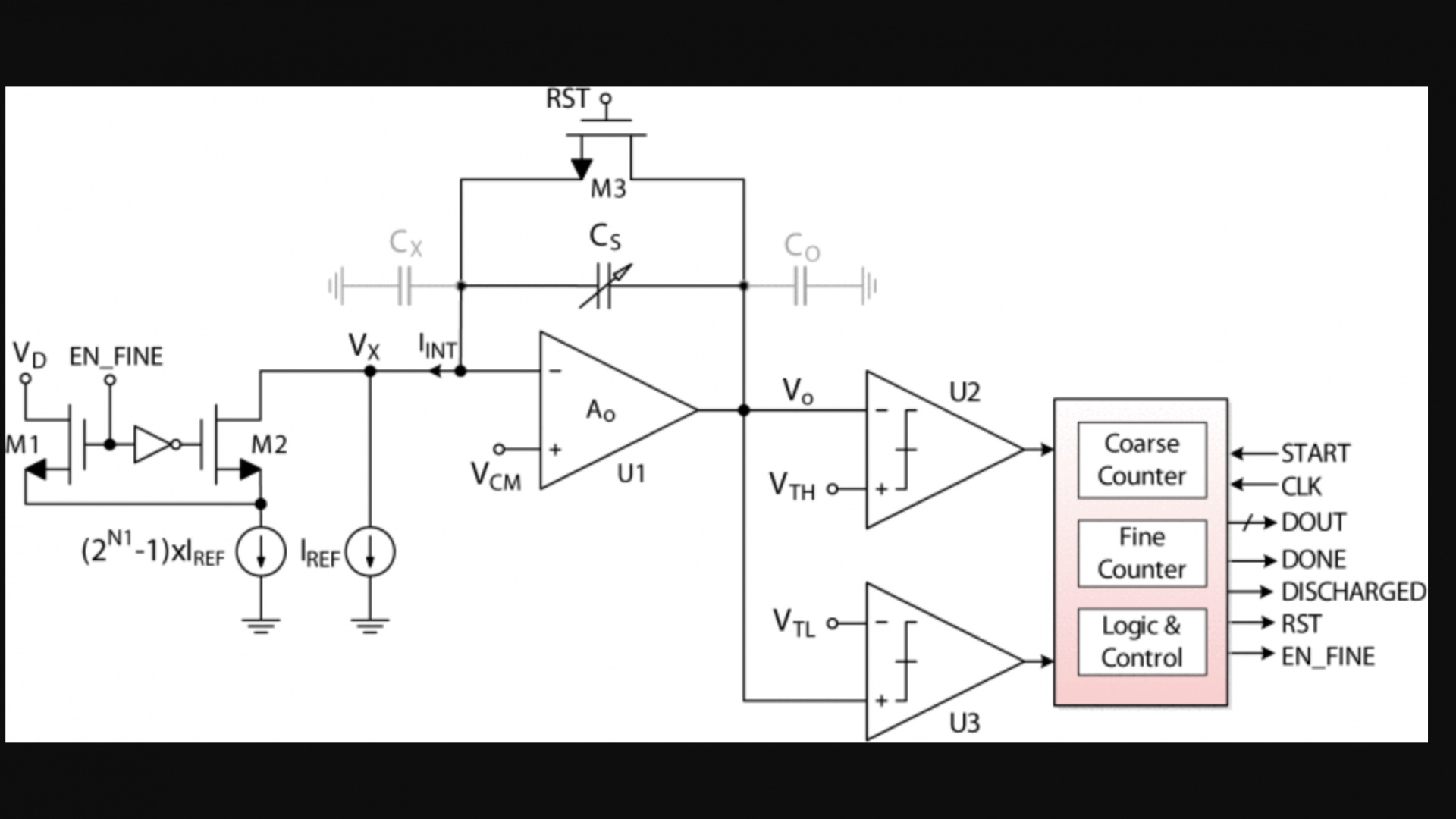

In this brief, an energy-efficient capacitance-to-digital converter (CDC) is presented. The proposed CDC uses digitally controlled coarse-fine multi-slope integration to digitize a wide range of capacitance in short conversion time. Both integration current and frequency are scaled, which leads to significant improvement in the energy efficiency of both analog and digital circuitry. Mathematical analysis for circuit nonidealities, noise, and improvement in energy efficiency is provided. A prototype fabricated in a 0.35-μm CMOS process occupies 0.09 mm 2 and consumes a total of 153 μA from 3.3 V supply while achieving 13-bit resolution. The operation of the prototype is experimentally verified using MEMS capacitive pressure sensor. Compared to recently published work, the prototype achieves an excellent energy efficiency of 7.9 pJ/Step.