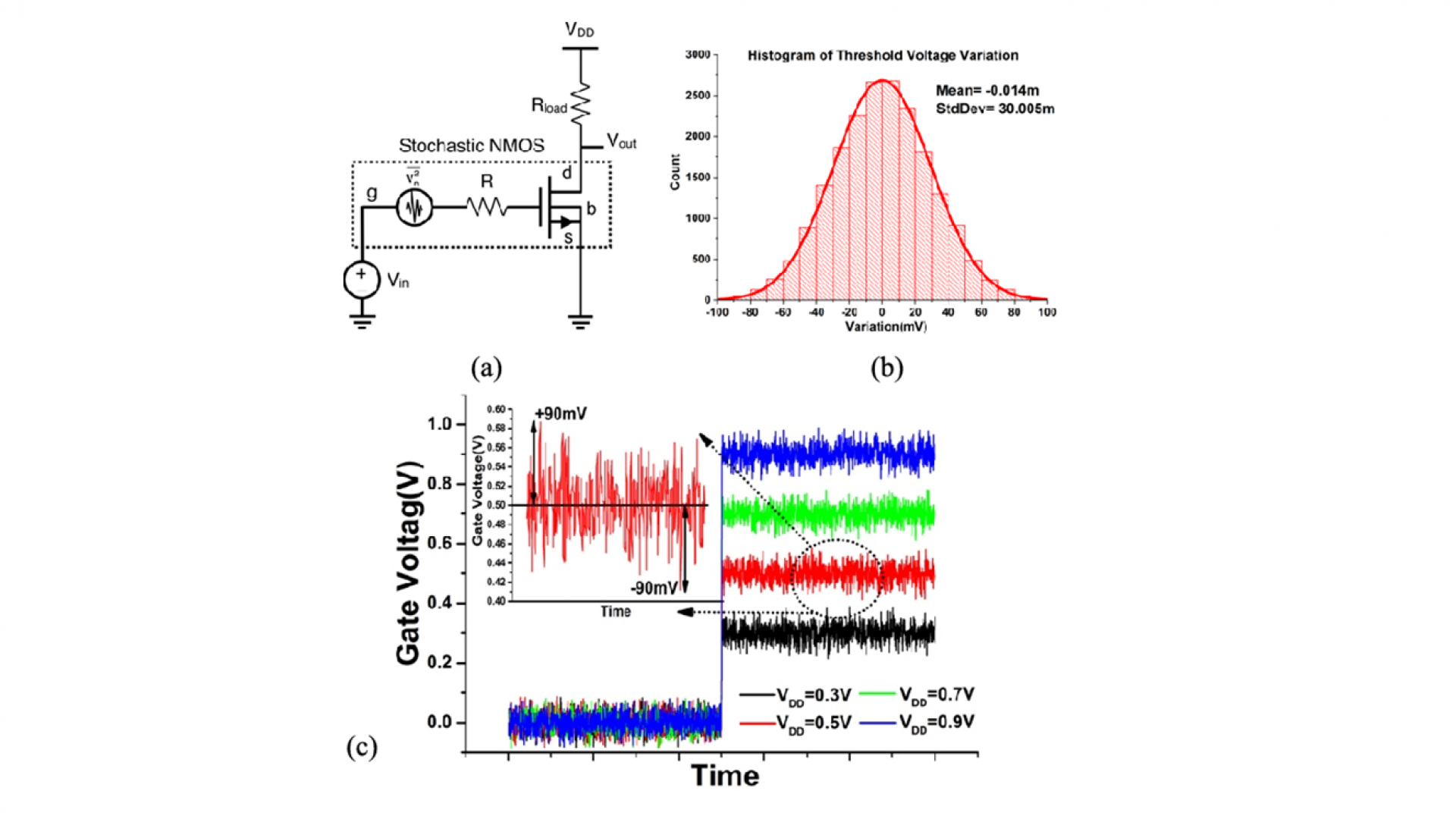

Ren Li, et al., "Approximate Computing With Stochastic Transistors’ Voltage Over-Scaling" IEEE Access 7, 2019, 6373.

Ubiquitous computing and the ever-rising need for energy efficiency pose challenges in terms of the processing requirements and the corresponding machine complexity. Nonetheless, the nature of the underlying applications, particularly dealing with real-world data, offers alternative paradigms toward the efficient utilization of the available design resources. In this paper, approximate computing is addressed as an accommodating technique that can benefit from the inherent resilience of the current applications to build low-power and low-complexity architectures. This paper proposes an alternative way of attaining approximation based on transistor dynamic variability. Furthermore, it presents a comprehensive study using voltage scaling scheme, starting from the impact of variation on the circuit-level output and investigating cascaded logic gates, storage elements, arithmetic building blocks, and on the application level, with an image compression outcome using 2-point discrete Fourier transform as a proof of concept. This paper addresses design analysis metrics and the efficiency of the proposed technique with respect to the technology node, operating frequency, energy and delay, process corner, and temperature. The configurable designs are shown to be possible with adaptive voltage scaling and energy-quality scalability. The proposed technique offers compromises in terms of the circuit design metrics with savings of up to 90% on energy for image compression application, in comparison with running at deterministic nominal value, while preserving the relative quality and accuracy of the output.