Hesham Omran, et al., "An integrated energy-efficient capacitive sensor digital interface circuit." Sensors and Actuators A: Physical 216, 2014, 43.

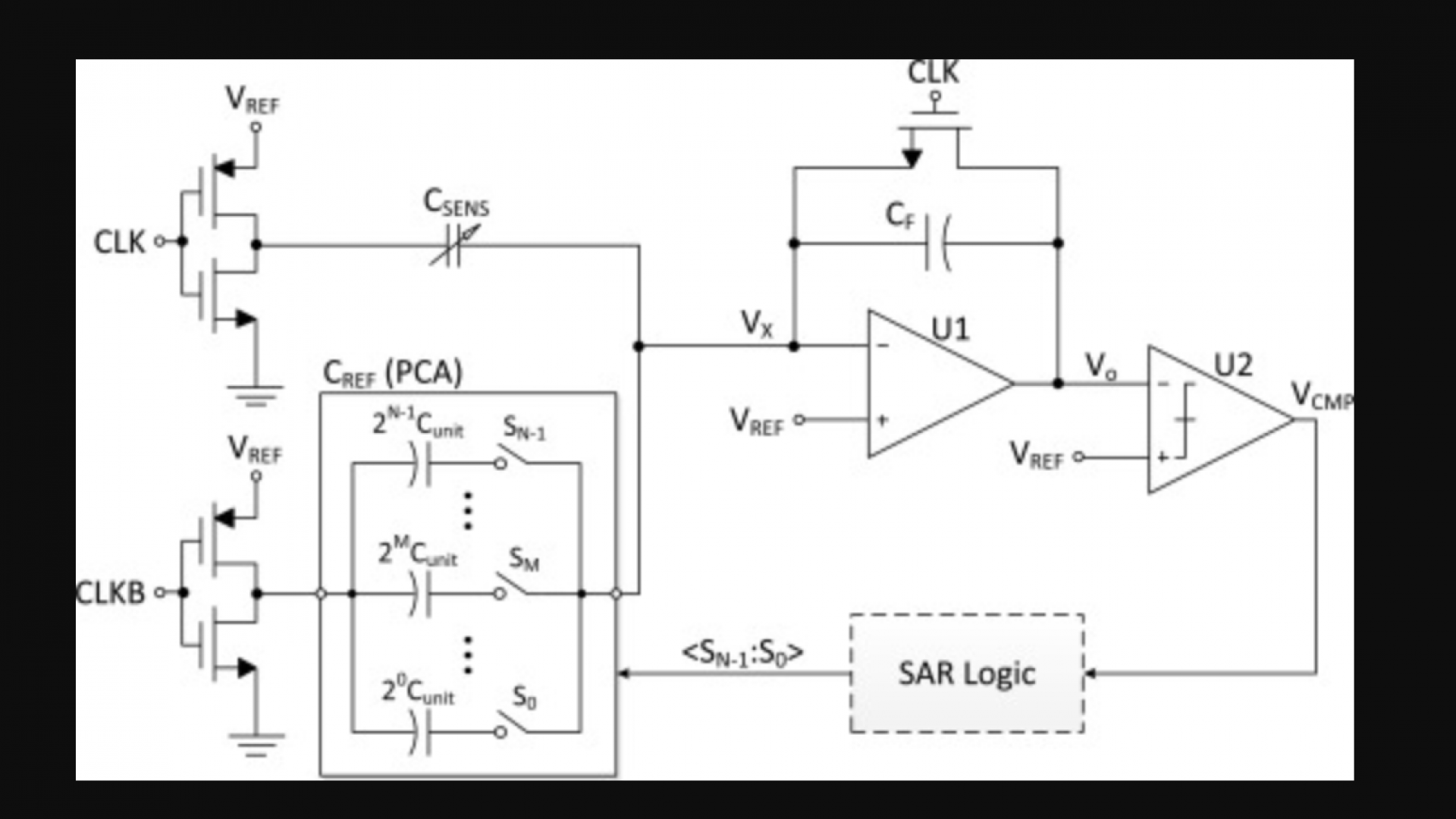

In this paper, we propose an energy-efficient 13-bit capacitive sensor interface circuit. The proposed design fully relies on successive approximation algorithm, which eliminates the need for oversampling and digital decimation filtering, and thus low-power consumption is achieved. The proposed architecture employs a charge amplifier stage to achieve parasitic insensitive operation and fine absolute resolution. Moreover, the output code is not affected by offset voltages or charge injection. The successive approximation algorithm is implemented in the capacitance-domain using a coarse-fine programmable capacitor array, which allows digitizing wide capacitance range in compact area. Analysis for the maximum achievable resolution due to mismatch is provided. The proposed design is insensitive to any reference voltage or current which translates to low temperature sensitivity. The operation of a prototype fabricated in a standard CMOS technology is experimentally verified using both on-chip and off-chip capacitive sensors. Compared to similar prior work, the fabricated prototype achieves and excellent energy efficiency of 34 pJ/step.