Ali H. Hassan, et al., "A New Design Methodology for Time-Based Capacitance-to-Digital Converters (T-CDCs)". AEU-International Journal of Electronics and Communications 96, 2018, 238.

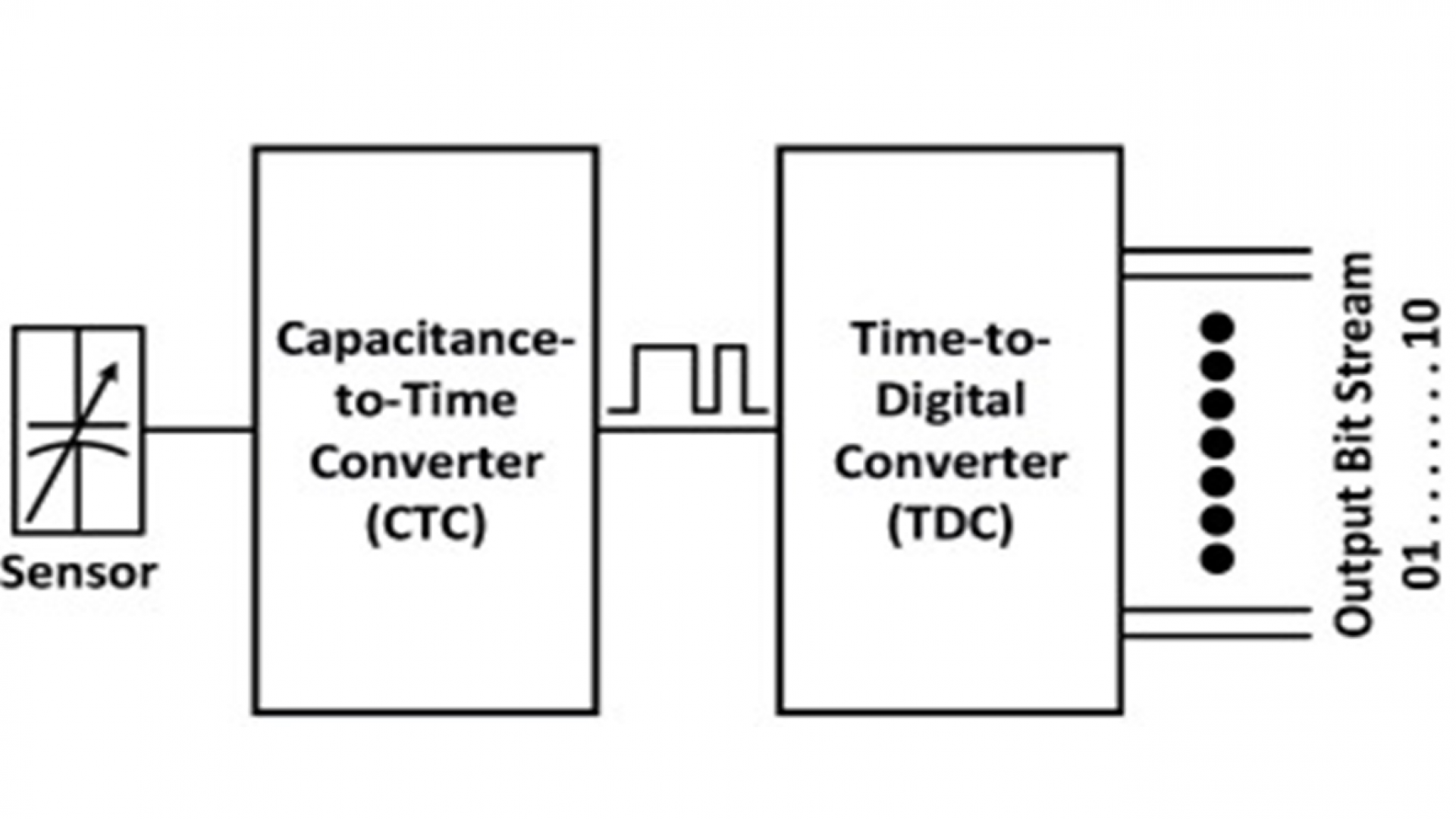

This paper introduces a 9-bit time-based capacitance-to-digital converter (T-CDC). This T-CDC adopts a new design methodology for parasitic cancellation with a simple calibration technique. In T-CDCs, the input sensor capacitance is first converted into a delay pulse using a capacitance-to-time converter (CTC) circuit; then this delay signal is converted into a digital code through a time-to-digital converter (TDC) circuit. A prototype of the proposed T-CDC is implemented in UMC 0.13 μm CMOS technology. This T-CDC consumes 8.42 μW and achieves a maximum SNR of 45.14 dB with a conversion time of 1 μs that corresponds to a figure of merit (FoM) of 16.4 fJ/Conv.