Reproduced with permission from reference 1© 2016

Resistive memory holds promise as an alternative memory architecture due to its high data density and high speed. However, even state-of-the-art "memristor" technologies are not sufficiently reliable and consume large amounts of power.

Khaled Salama and colleagues from KAUST have developed a memory reading scheme that negates the "sneaky" parasitic power losses responsible for this high power draw.

As the memory technologies used in modern computers approach their physical limits, further gains in performance are becoming increasingly difficult to achieve.

“Existing memory technologies such as SRAM and flash memory cannot achieve high speed and high data density at the same time,” explained Salama. “Memristor memories are about to change that, with both high speed and high density as well as lower fabrication cost.”

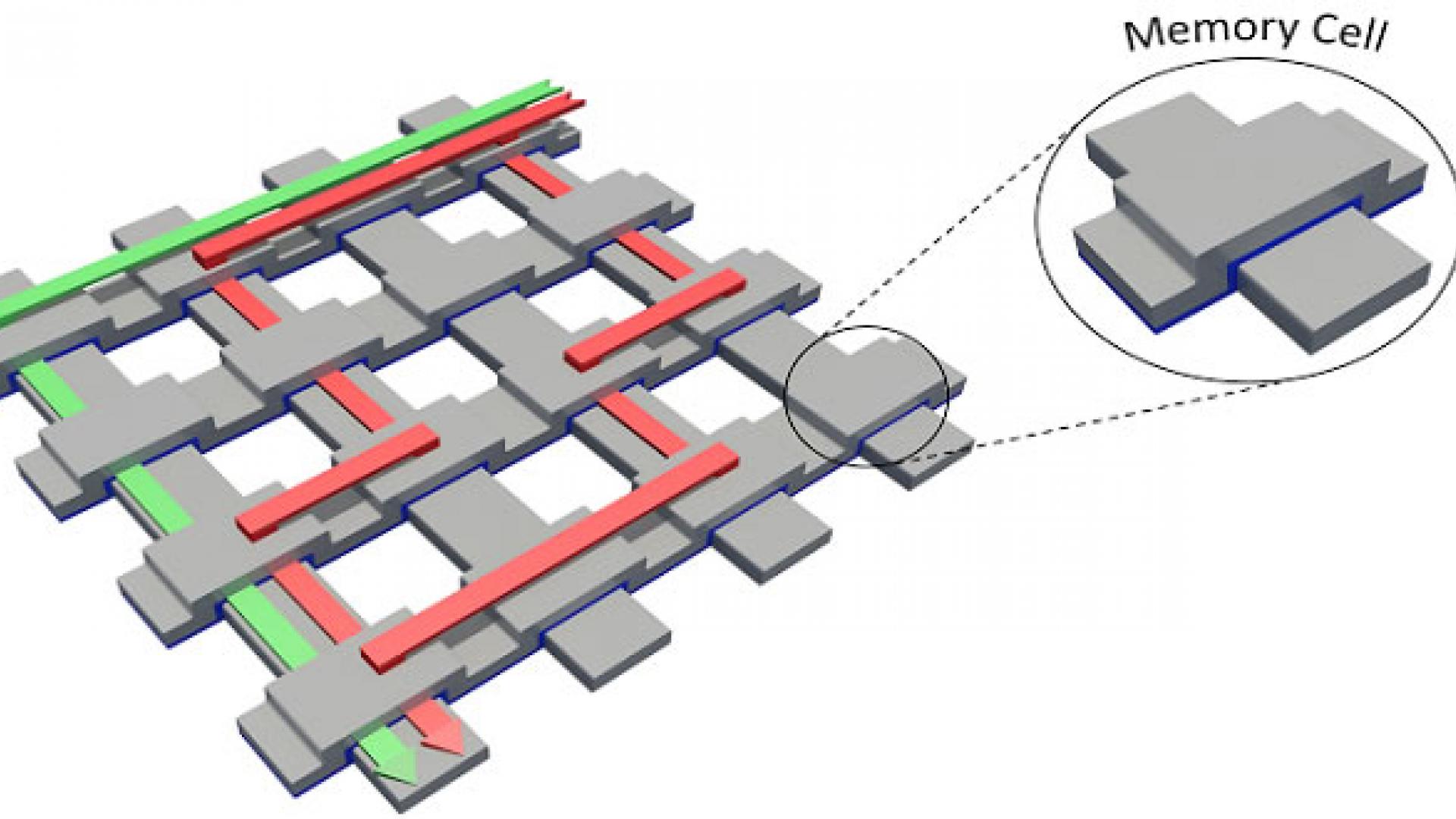

The memristor’s superiority comes from its simplicity. Essentially, it consists of a mesh of nanoscale interconnected wires called crossbars, where each intersection acts as a data bit by switching the resistance of the intersection high or low. The bits are then written and read by applying a current to the crossbars.

“While the simplicity of the structure is its principal advantage for fabrication and performance,” said Salama, “it is also the source of its main problem—that of sneak paths—which cause inaccurate, slow and energy-hungry data access.”

Read the full article