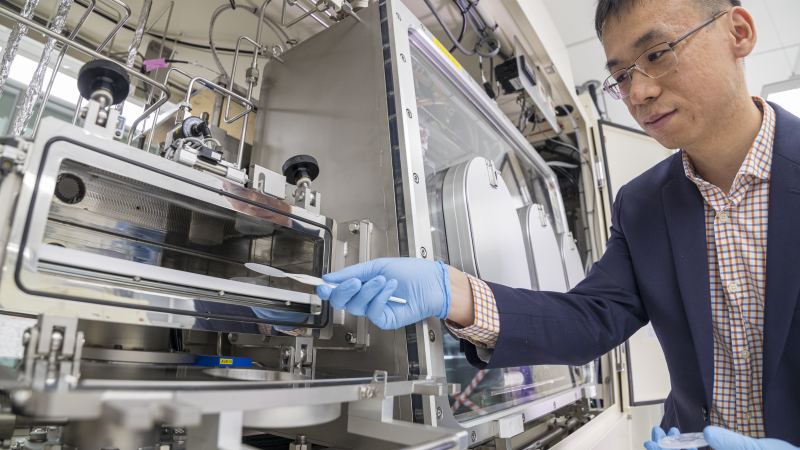

Zhiyuan Liu is a M.S./Ph.D. candidate in the KAUST Advanced Semiconductor Laboratory under the supervision of Professor Xiaohang Li. Before joining KAUST, Zhiyuan obtained a bachelor's degree in electrical engineering from the University of Electronic Science and Technology of China, China.

Research Interests

Zhiyuan's research interests focus on the modeling and fabrication of III-N semiconductor devices and the growth of III-N semiconductor materials